一、数字电子钟设计

1、设计任务及要求

(1)设计一个具有“时”、“分”、“秒”十进制数字的计数、译码、显示电路。

(2)电路具有校表功能

(3)由小规模的TTL芯片实现

2、仪器设备与元器件

(1)直流稳定电源

(2)信号发生器

(3)集成电路

74LS160 四位十进制同步计数器

74LS00 四2输入与非门

7448 BCD七段译码/驱动/锁存器

BS202 共阴数码显示器

二、系统设计思路与总体方案

(1)数字电子钟的设计原理

一个最简单的数字钟由秒信号发生电路,时、分、秒计数电路,译码显示电路组成,要求有校正时、分的功能,故要加入校时电路。因此其原理可由如下的框图表示出来。

振荡器产生的时标信号送到分频器,分频器将时标信号分成每秒一次的方波作为秒信号。秒信号送到计数器进行计数,并把累计的结果以“时”“分”“秒”的数字显示出来。“秒”的计数、显示由两级计数器和译码器组成的六十进制计数电路实现;“分”的计数、显示电路与“秒”的相同;“时”的计数、显示由两级计数器和译码器组成的二十四进制计数电路实现。所有的计时结果由六位数码管显示器显示。

(2)数字电子钟的工作原理

1、脉冲产生电路

秒脉冲产生电路由振荡器和分频器构成。振荡器有门电路构成的对称式多谐振荡器、环形振荡器以及由施密特触发器构成的多谐振荡器、石英晶体振荡器等多种类型。

数字电子钟应具有标准的时间源。用它产生频率稳定的1Hz脉冲信号,称为秒脉冲。

①由555定时器构成的秒脉冲产生电路如图所示:

周期计算公式:T=0.7(R1+2R2)C

频率为:f=1/T=1.45/(R1+2R2)C

R1 用330欧, R2用6.8K欧, C用0.1uF

555定时器第3脚输出的方波的周期:

T=0.7(R1+2R2)C=0.7x(0.33+2x6.8)x0.1 =0.9751

方波频率 F=1/T=1/0.9751=1.0255Hz

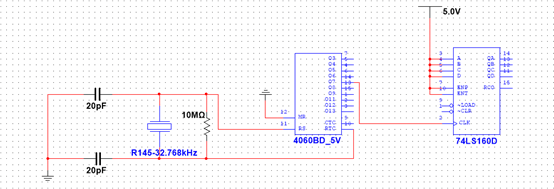

②由石英晶体振荡器产生的秒脉冲

数字电子钟通常采用石英晶体振荡器的谐振频率为32768Hz,经过二分频电路可得到频率为1Hz的秒脉冲信号。电路如图所示:

2、计数器

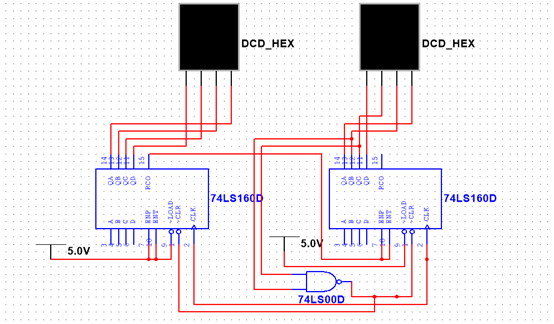

来自分频器的时标信号先后经过两级六十进制计数器和一个二十四进制计数器,分别得到“秒”个位、十位,“分”个位、十位及“时”个位、十位的计时。“秒”“分”计数器为六十进制计数器,“时”计数器分为二十四进制计数器。

六十进制计数器由两片74LS160组成,采用整体置零法来实现。

参考电路如图所示:

“时”计数器应为二十四进制计数器,也可采用两片74LS160芯片利用整体置零法来实现。当时计数器计数到第二十四个脉冲信号时,时计数器复位,即完成一个计数周期。电路图如图所示:

3、译码显示电路

译码电路可选用7448直接驱动共阴极的半导体数码管,下图为7448驱动BS202的译码显示电路。

4、校准电路

校准电路是当计时器刚接通电源或时钟走时出现误差时,进行时间的校准。

这里提供两个方案供参考:

方案一:

该电路由二级门电路和两个开关组成,用以实现对“秒”的校准。开关选择有“正常”和“校准”组成,左边的开关U33作为秒校准控制开关,当左开关为“0”时,脉冲信号不能进行传输,同时U32A被打开,按动U34开关会进行计数校准。

当U33开关为“1”时,秒计数器进行正常计数。

小时校准、分校准与秒类似,只不过时校准的脉冲信号是分产生的进位信号,分产生的进位信号是秒产生的进位信号,原理类似。

完整的电路图为:

方案二:

原理如下:(感谢@Ke提供的思路)

当ABC=000时,3个校准电路右下方的与非门打开,电路进行正常的计数

当ABC=001时,秒脉冲被封锁,左边的与非门打开,校准脉冲起到校准秒的作用

时校准、分校准与之同理。

完整电路图如下:

三、收获与体会

通过这次自己设计数字电路,虽然花费的时间很长,但学到了很多。第一,巩固和加深了对电子线路基本知识和理解,提高了综合运用所学知识的能力。第二,增强了根据课程需要选学参考资料,查阅手册,图表和文献资料的自学能力。通过独立思考,深入研究有关问题,学会自己分析解决问题的方法。第三,通过实际电路方案的分析比较,设计计算,元件选取,安装调试等环节,初步掌握了简单实用电路的分析方法和工程设计方法。第四,掌握了比较常用的仪器的使用方法,提高了动手能力。第五,培养了严谨的工作作风和科学态度。

Comments 2 条评论

站长真的很屌大家快来支持赵站长!!!!!!!!

@CR